|

|

|||

|

CIRCUITI SEQUENZIALI |

|||

|

|||

|

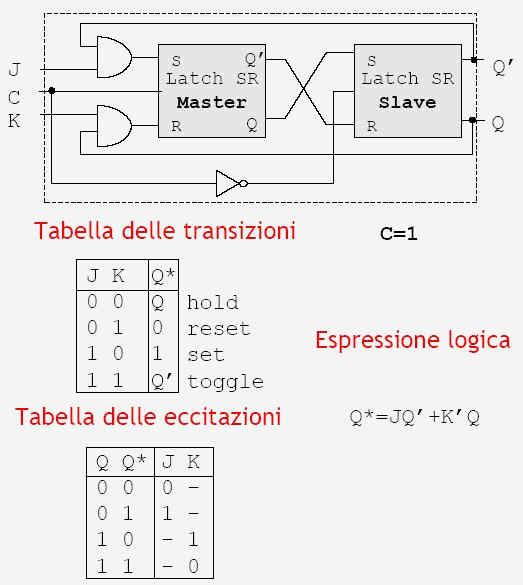

FLIP FLOP I latch, spesso, non consentono di garantire un comportamento affidabile nella realizzazione di una data funzionalità. Per evitare l’effetto di propagazione indesiderata, i bistabili sincroni vengono modificati in modo che lo stato possa modificare le uscite solo in corrispondenza di un evento (fronte) del segnale di controllo. Si parla quindi di Flip-Flop: – Relazione stato-uscita (aggiornamento della uscita): sul fronte– Relazione ingresso-stato (aggiornamento dello stato):

Flip-Flop: Master-Slave I

flip-flop master-slave vengono realizzati utilizzando due latch in

cascata che hanno il segnale di sincronismo in contrapposizione di fase

– Il primo latch sincrono è chiamato latch principale (master). – Il

secondo latch sincrono è chiamato latch ausiliario (slave). – I due

latch lavorano in contrapposizione di fase - il percorso di

propagazione ingresso uscita non è continuo.

Fig. 6: latch di tipo JK MasterSlave

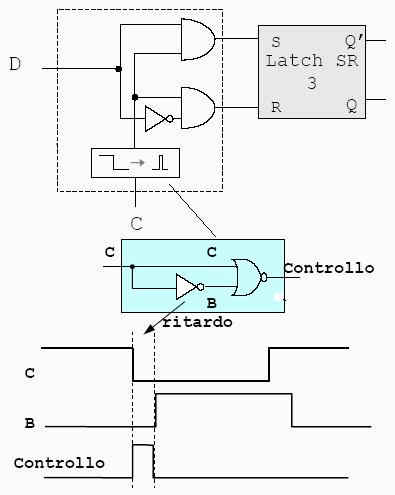

Flip-Flop Edge-Triggered I flip-flop Edge-Triggered vengono realizzati producendo (con un circuito analogico o digitale) la derivata del segnale di clock: si genera un impulso (fisico o funzionale) in corrispondenza di un fronte. In figura7 e' mostrato un FF di tipo edge triggered.

Fig. 7: latch di tipo Flip-Flop Edge-Triggered Per C=1

gli ingressi del Latch SR 3 sono S=0 e R=0. Per C=1->0, il valore su

D attiva il latch SR 1 e, successivamente, viene attivato il latch SR

2. Se D=1, il segnale Q del latch SR 1 viene portato a 1; se D=0 il

segnale Q del latch SR 1 resta a 0. |

|

||

|

|

|||