|

|

|||

|

DAC: ARCHITETTURE DI BASE - 4 |

|||

|

|||

|

|

|||

|

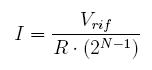

Architetture DAC Ibride Le architetture dei convertitori digitali analogici, discusse precedentemente, presentano una serie di vantaggi e di svantaggi. Una combinazione di tecniche differenti può essere utilizzata, pertanto per migliorare le prestazioni di un DAC. Tali architetture sfruttano un certo numero di subconvertitori DAC che possono essere di tipo diverso. Una delle strutture ibride più conosciute e' la cosiddetta architettura segmentata. In essa i MSB sono codificati in codice termometrico e i LSB sono a peso binario. L’aspetto fondamentale di questo tipo di struttura e' la ricerca del numero ottimo di bit da codificare in codice termometrico. In questo caso, il conseguente aumento dei circuiti digitali, del rumore, dell’area, ecc., hanno un’importanza rilevante. Famiglie di Convertitori Digitali Analogici Possiamo considerare tre grandi famiglie di DAC: • In tensione • In corrente • A ridistribuzione di carica I convertitori a ridistribuzione di carica rientrano, tuttavia, nella prima famiglia (voltage-mode). In ciascun tipo di DAC la variabile sotto cui e' codificata l’informazione e' rispettivamente una tensione, corrente o carica. In un DAC in tensione(corrente), i suddetti elementi saranno rappresentati da correnti (in questo caso, per esempio generatori di corrente commutati o resistori dividono una corrente piu' grande in un certo numero di sottocorrenti pesate). Infine, i DAC a ridistribuzione di carica utilizzano come elementi, dei capacitori. Poiche' la specifica del convertitore in esame richiede una elevata velocita', la famiglia dei DAC in corrente sara' quella alla quale faremo riferimento in questa tesi. DAC a Resistori Pesati Per motivi di comprensione, e' bene riportare la caratteristica di trasferimento di un DAC che utilizza un codice binario: dove D = V0/Vrif , bi 2 {0, 1} ed N e' il numero di bit utilizzati. Il peso del MSB b1, vale cos`i Vrif/2 mentre il peso del LSB bN, vale Vrif/2N. L’uscita sara' nulla quando tutti i bit sono spenti, ovvero quando tutti gli ingressi sono posti a 00000, mentre varra' V0 = Vrif · (1 - 2-N) se gli ingressi sono posti a 00100. E’ bene notare che nella (2.4), i termini sono sommati e il peso di ogni termine si ottiene dal precedente moltiplicandolo per 1/2. Pensiamo, così, di realizzare una configurazione circuitale del tipo indicato in figura. Essendo il morsetto invertente una massa virtuale, la corrente che scorre nei resistori sarà: se il bit corrispondente e' basso (00000). L’amplificatore operazionale sta funzionando come convertitore corrente-tensione a bassa impedenza d’uscita. I problemi maggiori di questo tipo di circuito sono, principalmente di due ordini: 1. le resistenze dei bit posti a 00000 non scaldano, come invece fanno le resistenze dei bit posti ad 00100, quindi, a causa del coefficiente di temperatura e dell’inerzia termica, presenteranno dei valori, in rapporto, differenti dai nominali. 2.

E’ difficile riuscire a costruire resistori, seppur integrati, che

stiano, correttamente,

in un dato rapporto gli uni con gli altri. E’ facile, invece, costruire

resistori uguali.

Per

ovviare al primo problema possiamo modificare il circuito decidendo di

far sempre

scorrere una corrente in tutte le resistenze, ovvero, mantenendole

sempre preriscaldate.

Per ovviare, invece, al punto 2, bisogna rifarsi ad un’altra topologia

circuitale basata

sulle reti a scala R-2R (ladder network) che presentano attenuazione e

resistenza

costante. |

|

||

|

|

|||

|

|

|||

|

|

|||