|

SONDA

LOGICA CMOS - 2 |

|||||||

|

|||||||

|

|

|||||||

|

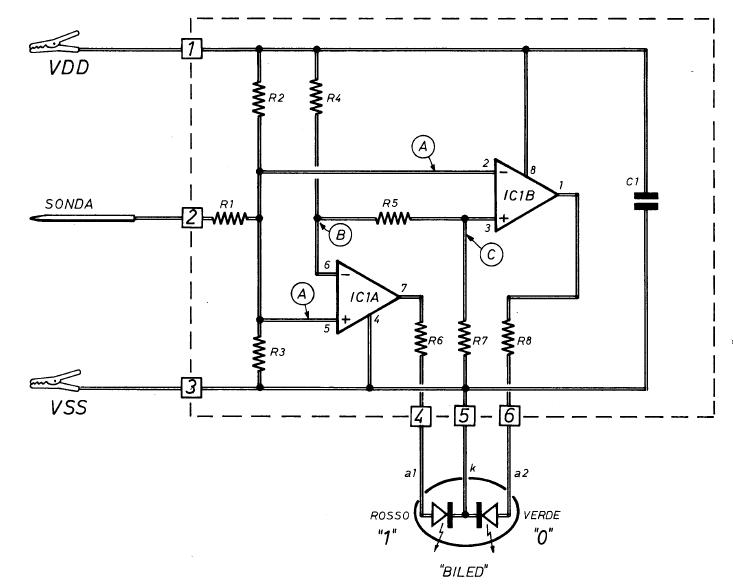

CIRCUITO DELLA SONDA CMOS Il circuito della sonda, cioè dell'indicatore di stato logico dei circuiti CMOS, e’ quello riportato in figura 1.

Fig. 2 - Circuito elettrico dell'indicatore di stato logico per dispositivi in cui sono montati gli integrati CMOS.

COMPONENTI

Esso

utilizza un integrato di tipo LM358 P, il quale e’ contenuto in un

elemento plastico ad otto piedini e può essere assimilato a due

distinti amplificatori operazionali di tipo uA74l (IC1A - IC1B). Ma

l’integrato LM 358 P si differenzia dall'operazionale upA741 per la

diversa gamma di tensioni di alimentazione. In particolare, l’LM 358 P

può funzionare con tensioni basse come i CMOS. Ma passiamo senz'altro

all'esame del funzionamento del circuito di figura 1. Le resistenze R2

- R3 stabiliscono il valore della tensione sul punto A. Tuttavia,

essendo queste di uguale valore, ossia di 1 mega-ohm, sul punto A e’

presente la tensione positiva di alimentazione VDD (figura 4) divisa

per due. Facciamo un esempio: se il circuito e’ alimentato con la

tensione di 12 V, sul punto A sono presenti 6 V. Ma, attenzione! Per

misurare questi 6 V, non e’ possibile servirsi di un tester normale,

mentre occorre utilizzare un tester elettronico con impedenza

d'ingresso elevata, che non carichi la resistenza R3. Se si utilizza un

normale tester analogico, da 20.000

ohm x volt, si rileva il valore di tensione di 1V – 2V, ovviamente

senza alcun segnale applicato all'entrata. Con il voltmetro

elettronico, mantenendo valido l'esempio citato, si rilevano i seguenti

valori di tensioni nei punti A - B - C del circuito: 6 V - 7,3V - 4,8

V. |

|

||||||

|

|

|||||||

|

|

|||||||