|

|

|||

|

CONVERTITORE

ANALOGICO DIGITALE SERIALE - 2 |

|||

|

|||

|

|

|||

|

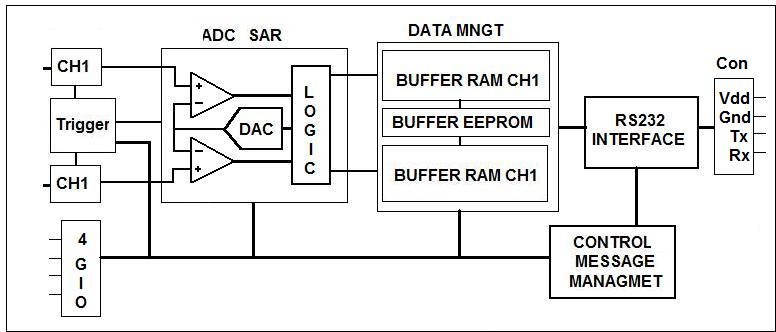

Schema a Blocchi In figura 1 è riportato lo schema a blocchi del convertitore analogico digitale .

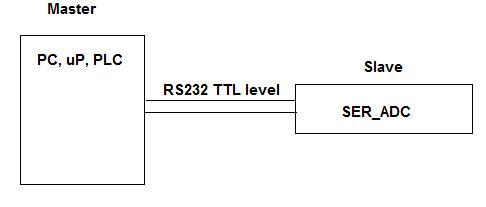

Figura 1: schema a blocchi del convertitore A/D seriale Come si vede dalla figura 1 il convertitore seriale contiene diverse strutture al suo interno: Lo stadio di ingresso e' composto dai due canali CH1 e CH2 assieme al Trigger. Lo stadio di uscita e' rappresentato dal blocco che gestisce le 4 uscite di uso generico indicate con GIO. Il cuore del convertitore e' rappresentato dal convertitore SAR (ADC SAR) a 10 bit che converte i segnali dei canali CH1 e CH2 mettendo il risultato della conversione sui rispettivi buffer RAM ( RAM CH1 e RAMCH2). Entrambi i buffer RAM possono essere letti dall'esterno ( funzioni F3 e F4), riversare il loro contenuto sul buffer EEPROM ( funzioni F7 e F8) o importare da esso il suo contenuto (funzione F9). La comunicazione con l'esterno e' gestita da unita di controllo che e' costituita da un interfaccia che gestisce il protocollo RS232 e da un gestore dei messaggi in ingresso e di uscita. Collegamento di sistema del convertitore Il convertitore e’ utilizzabile in un sistema di tipo MASTER - SLAVE. Esso ha caratteristica di SLAVE. Il MASTER deve occuparsi di controllare il flusso di dati da e verso il convertitore. Tutte le operazioni del convertitore saranno dunque conseguenza di un messaggio di comando proveniente dal Master.

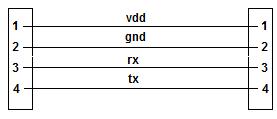

Fig.2 Sistema di connessione Master- Slave del convertitore Il master può essere rappresentato da un sistema composto da micro con un firmware che implementa il protocollo di comunicazione o da un PC su cui gira un software ( Labview, C, Visual Basic) che pilota la seriale e che implementa il protocollo. BUS di collegamento Per pilotare il convertitore si utilizza un bus a 4 fili ( Gnd , Vcc, rxdata, txdata) che contiene sia il fili per la comunicazione sia l’alimentazione che deve essere fornita dal sistema Master che lo controlla.

Fig.3 - collegamento del convertitore al master

|

|

||

|

|

|||

|

|

|||

|

|

|||