|

Generatore di frequenza variabile - 2 |

|||

|

|

|||

|

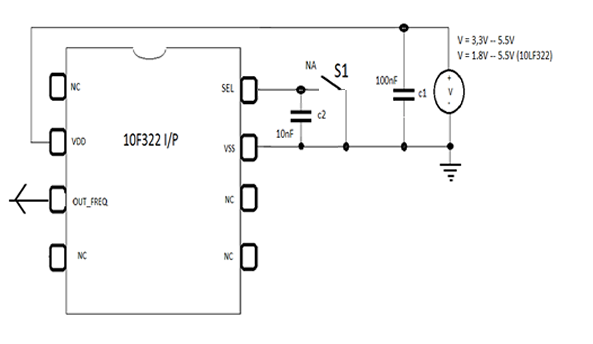

Implementazione hardware L'implementazione hardware del generatore di frequenza variabile e' molto semplice. L'unico componente esterno e' il pulsante con cui effettueremo la selezione della frequenza da generare. Il circuito di alimentazione e' il classico che richiede l'utilizzo tensione continua stabilizzata che può variare da un valore di 3,3V a 5,5V (1,8V a 5,5V per la versione LF). avendo cura di mettere un condensatore da 100nF tra i pin di VDD e VSS del micro e in parallelo al pin SEL un condensatore di almeno 10hìnF per filtrare i rimbalzi dovuti al pulsante pulsante. Di seguito lo schema elettrico del circuito del generatore di frequenza variabile:

Implementazione firmware A livello di firmware la realizzazione del progetto e' molto semplice. Le periferiche da configurare sono l'oscillatore e le GPIOs. Dal datasheet si evince che il pin dedicato per l'uscita del clock di sistema e' il pin RA2 che fa capo al pin 3 del micro ( riferito al package DIP8). L'uscita del segnale sul pin CLKR si ottiene settando il bit CLKROE del registro dedicato OSCCLK. Il valore della frequenza da usare come clock di sistema e quindi da buttare fuori e' definito con il registro OSCCON tramite i suoi 3 bit IRCFS<2:0>. Il pin, che useremo come ingresso di selezione da collegare ad un pulsante esterno e' il pin 8 che e' per default il pin di (MCLR= master clear).Questo pin lo chiamiamo SEL. e lo scolleghiamo dalla funzione di MCLR tramite il bit di configurazione del microcontrollore (MCLR_OFF) ed lo definiamo come ingresso con pull-up interno. La routine di selezione legge lo stato del pin SEL. Se questo pin ha un valore basso (pulsante premuto ) si aspettano 10 ms e, se alla fine di questo tempo, il pin SEL e' ancora basso allora si passa ad incrementare il valore dei bit IRCF di selezione nel registro OSCCON. La routine esce se il pin SEL e' rilasciato e torna nel uso stato di riposo che corrisponde ad un valore alto ( pulsante non premuto). Un accorgimento da tenere e' sulla routine di delay da 10ms. Poiché questo e' basato sul clock di sistema ogni qualvolta cambiamo il clock di sistema in base alla selezione avremo di avere dei tempi non uguali falsando l'utilità di questo delay. Per quando si richiama la routine di delay si riporta il clock di sistema ai valori per cui la routine di delay genera un delay di 10ms memorizzando il valore attuale della selezione di frequenza in una variabile temporale ( nel codice e' la variabile TEMP). Appena finisce la routine si riporta il valore della selezione tenendo condo del cambiamento dovuto alla routine di selezione. Di seguito il codice in assembler del nostro oscillatore variabile. |

|

||

|

|

|||

|

|

|||